# Lean NPI driven by Test coverage

**TestWay Express** is a fully integrated solution that enables electronic manufacturers to optimize the design to test flow:

- Define the manufacturing line; including a combination of assembly, inspection and test machines.

- Estimate the test coverage of each individual stage and optimize the combined results.

- Generate the input files for each test stage that reflect the selected strategy.

- Measure the real test coverage by importing the post-debug test program or coverage data.

- Compare the early estimation with the actual measured test program coverage, identifying gaps in the overall strategy.

Test is essential for improving product quality by striving to detect and prevent all faults on a product. This maximizes the number of good products shipped to the customer. It is important to:

- Define the optimum test strategy to maximize the test coverage.

- Produce a test specification document that defines what to test.

- Compare the developed tests against the test requirements.

- Understand the production process capability and determine an acceptable level of defects that can be shipped to the customer.

**TestWay Express** analyzes the number of defects detected at each stage in the test process and identifies any shortfall in test coverage and undetected defects. It allows the computation of the IPC metrics such as first pass yield (*FPY*), fall-of-rate or escape rate by importing the real time DPMO (*Defect Per Million Opportunities*) from the manufacturing process. The manufacturing test strategy is tuned to provide the optimal test coverage for identifying potential defects.

**TestWay Express** is built around TestWay<sup>™</sup>, the industry leading DfT and test coverage analysis platform from the ASTER product portfolio.

## EASE OF USE

A combination of application wizards, and drag and drop operations guide you through the project creation, to enable coverage reports to be generated in 6 easy steps:

- Input the board data.

- Modelize the components.

- Place the probes.

- Select the manufacturing strategy.

- Generate input files for test & inspection machines.

- Create the test coverage reports.

www.aster-technologies.com

#### Key product benefits

#### • Ease of Use

Application wizards guide you through the project. Add multiple test strategies for project analysis, by a simple drag and drop from the machine list.

• **Probe allocation & accessibility** Place probes exactly where required with a comprehensive set rules to define priorities, clearances and constraints, and generate detailed accessibility report.

#### • Test coverage estimation

- Maximize test and inspection coverage, by estimating coverage of selected test strategies. Perform "what-if" analysis to select the optimal test strategy and achieve maximum coverage. Eliminate redundant test steps.

- Automated test program creation Generate the input files for Assembly, AOI, AXI, BST, ICT and FPT machines in a matter of minutes or hours rather than days.

- Test coverage measurement Determine the real test coverage and compare against the early estimation, to identify areas for improvement.

- Yield estimation

Calculate the first pass yield (FPY) by importing real time DPMO data for the manufacturing process, to tune the test strategy for optimum test coverage.

• Wide variety of testers supported

Import & Export test programs from a wide range of vendors, more than 50 test & inspection machines supported.

- Layout from native CAD formats Create layout view from standard CAD formats such as GENCAD, CAMCAD, FATF, ODB++, or direct from native CAD layout data.

- Component classification Visualize and edit component attributes such as part number, shape, class, value, tolerance, mounted status, etc. Prompts for missing information.

## **INPUT BOARD DATA**

Over 60 CAD importers are available to support layout, schematic netlist and schematic graphics. This is a key differentiator, as other commercial DfT tools work only from the layout stage.

**TestWay Express** operates from native CAD formats and ensures full interoperability between all stages across the design/manufacturing flow.

CAD data is required to understand the board design. Geometric and electrical information, such as component class, value, tolerance, package shape and height, are automatically extracted.

The probe locations are referenced when assessing the nodal access for flying probe and in-circuit, during test program generation or coverage analysis.

The Bill Of Material *(BOM)* can be used to supplement the CAD data with additional attributes that may not be provided in the CAD data, such as part number, component description, value, mounted status, etc.

The board schematic can be imported to allow full interaction between the reports and the viewer and to visualize any attributes such as test coverage.

# MODELIZE THE COMPONENTS

The better the components are modelized, the more accurate is the test strategy analysis.

| 3 | Gro   | iup by: | None       | ~     | 42      | ■ 8 A                 |       |       |      |       |            |        |           |

|---|-------|---------|------------|-------|---------|-----------------------|-------|-------|------|-------|------------|--------|-----------|

|   | Ref   | Туре    | PartNumber | Shope | Fin cat | Closs                 | Value | NTol  | PTol | SPUT  | Model tile | Tested | Mounted ? |

| 1 | C7020 | FAR.    | FARNELL.   | CAPC  | 2       | HE CAPACITORIANALOG   | 100n  | -10   | 10   |       |            |        | Yes       |

| 1 | C7021 | FAR.    | FAPNELL.   | CAPC  | 2       | + CAPACITORIANALOG    | 100n  | -10   | 10   |       |            |        | Yes       |

| 1 | C7022 | FAR.    | FARNELL    | CAPC  | 2       | HE CAPACITORIANALOG   | 100n  | -10   | 10   |       |            |        | Yes       |

| 2 | C7023 | FAFL    | FARNELL.   | CAPC  | 2       | HE CAPACITORIANALOG   | 100n  | -10   | 10   |       |            |        | Yes       |

| 1 | C7024 | FAR.    | FARNELL.   | CAPC  | 2       | HE CAPACITORIANALOG   | 100n  | -10   | 10   |       |            |        | Yes       |

| 1 | C7025 | FAR.    | FAPNELL    | CAPC  | 2       | HE CAPACITORIANALOG   | 100p  | -5.00 | 5.00 |       |            |        | Yes       |

| 1 | C7026 | FAR.    | FARNELL.   | CAPC  | 2       | HE CAPACITORIANALOG   | 100p  | -5.00 | 5.00 |       |            |        | Yes       |

| 2 | C7027 | FARL.   | FARNEUL.   | CAPC  | 2       | HE CAPACITORIANALOG   | 100p  | -5.00 | 5.00 |       |            |        | Yes       |

| 1 | C7028 | EAR.    | FARNELL    | CAPC  | 2       | HE CAPACITORIANALOG   | 100p  | -5.00 | 5.00 |       |            |        | Yes       |

| 2 | C7029 | FARL.   | FARNEUL    | CAPC  | 2       | HE CAPACITORIANALOG   | 100p  | -5.00 | 5.00 |       |            |        | Yes       |

| 1 | C7030 | FAR.    | FARNELL.   | CAPC  | 2       | HE CAPACITORIANALOG   | 100p  | -5.00 | 5.00 |       |            |        | Yes       |

| 2 | C7031 | FAR.    | FAPNELL.   | CAPC  | 2       | HE CAPACITORIANALOG   | 100p  | -5.00 | 5.00 |       |            |        | Yes       |

| 1 | D600  | FAR     | FARNELL.   | LEDCI | 2       | (> LED,DIODE,HYBPID   | HS    |       |      | [1,2] |            |        | Yes       |

| 7 | D601  | FARL.   | FARNELL.   | LEDC1 | 2       | ♦ LED.DIODE.HYBRID    | HS    |       |      | [1.2] |            |        | Yes       |

| 1 | D602  | FAR.    | FARNELL.   | LEDC1 | 2       | IF LED, DIODE, HYBRID | HS    |       |      | [1,2] |            |        | Yes       |

| 7 | D603  | FAR.    | FARNELL.   | LEDC1 | 2       | ♦ LED.DIODE.HYBRID    | HS    |       |      | [1.2] |            |        | Yes       |

| 1 | D604  | EAR.    | FARNELL.   | LEDCI | 2       | ↓ LED,DIODE,HYBRID    | HS    |       |      | [1.2] |            |        | Yes       |

| 2 | D605  | FAFL.   | FARNELL.   | LEDC1 | 2       | ♦ LED.DIODE.HYBRID    | HS    |       |      | [7.2] |            |        | Yes       |

| 1 | D606  | FAR.    | FARNELL.   | LEDC1 | 2       | IED,DIODE,HYBPID      | HS    |       |      | [1.2] |            |        | Yes       |

| 2 | D607  | FAR.    | FARNELL.   | LEDC1 | 2       | H LED.DIODE.HYBRID    | HS    |       |      | [1.2] |            |        | Yes       |

| 1 | D608  | FAR.    | FARNELL.   | LEDC1 | 2       | IED,DIODE,HYBRID      | HS    |       |      | [1,2] |            |        | Yes       |

| 1 | D609  | FARL.   | FARNELL.   | LEDC2 | 2       | ♦ LED.DIODE.HYBRID    | HS    |       |      | [1.2] |            |        | Yes       |

The component classificator is a user friendly editor that allows users to:

- Edit component type, value, tolerances, part number, etc, required to determine the type of test that can be conducted on the component.

- Define pin function of polarized components and internal component structures for multi-element components, such as resistor packs or double diodes.

- Import BSDL files to describe the boundary-scan cell structure of boundary-scan compliant devices.

- Re-use component or test models, in order to specify component and pin attributes.

A component wizard is provided to simplify the component modeling, automatically identifying device classes, importing any available models and extracting valuable component information, such as value, tolerance, shape etc, directly from the BOM description.

# PLACE THE PROBES

Probe Analyzer

Probes are placed by considering the mechanical and design for test (*DfT*) constraints practiced by respective companies.

| Profile Priority rules Constra | ints Setup | Probe Size Probe Quantit    | y Display Rules  |

|--------------------------------|------------|-----------------------------|------------------|

| Unit                           | mm         | ¥                           | Shape detritions |

| Tester Type:                   | Fodure     | ) Fixtureless               |                  |

| Minimum Feature Size           | 0.7        | SMD Pin Offset              | 0.3              |

| Package Outline Clearance      | 0.6        | Apply offset on SMD         |                  |

| Board Outline Clearance:       | 1 27       | Apply affset an Test Pain   | 68 🗌             |

| Feature Clearance:             | 1 905      | Apply affset an THT pins    |                  |

| Tooling Hole Clearance:        | 254        | Minimum drill size for offs | et: 0.3          |

| Ignore mount status:           |            | No offset on lifted corts   |                  |

| Ignore Mechanical net:         |            | Use solder mosk:            |                  |

| Include One-Pin Net:           |            | Solder mask tolerance.      | 0                |

| Include Multiple Pin Net:      |            | Keep alternate no is:       |                  |

Probe locations may already be defined within the CAD data, but there may be insufficient access for maximum test coverage. In which case the probe analyzer can be used to consider alternative accessibility options, such as through hole pins (*THT*), connectors, SMD pads, vias or bead probes etc.

X

| 1 | Probing side                  | Object                  |                                       | Size            | Filter            |                                           |                        |                                         |                       | ŵ          |

|---|-------------------------------|-------------------------|---------------------------------------|-----------------|-------------------|-------------------------------------------|------------------------|-----------------------------------------|-----------------------|------------|

|   | Bottom                        | Test_Po                 | int 1                                 | Defaul          | t                 |                                           |                        |                                         |                       |            |

|   | Bottom                        | Connect                 | or I                                  | Defaul          | it                |                                           |                        |                                         |                       | ×          |

|   | Bottom                        | THT                     | 1                                     | Defaul          | t                 |                                           |                        |                                         |                       |            |

|   | Тор                           | Test_Po                 | oint I                                | Defaul          | t                 |                                           |                        |                                         |                       |            |

|   | Тор                           | Connect                 | or I                                  | Defaul          | t                 |                                           |                        |                                         |                       |            |

|   | Тор                           | THT                     | 1                                     | Defaul          | it                |                                           |                        |                                         |                       |            |

| * |                               |                         |                                       |                 |                   |                                           |                        |                                         |                       |            |

|   |                               |                         |                                       |                 |                   |                                           |                        |                                         |                       |            |

|   |                               |                         |                                       |                 |                   |                                           |                        |                                         |                       |            |

|   |                               |                         |                                       |                 |                   |                                           |                        |                                         |                       |            |

|   |                               |                         |                                       |                 |                   |                                           |                        |                                         |                       |            |

|   |                               |                         |                                       |                 |                   |                                           |                        |                                         |                       | T.         |

|   |                               |                         |                                       |                 |                   |                                           |                        |                                         |                       | Ŷ          |

|   |                               |                         |                                       |                 |                   |                                           |                        |                                         |                       | Ŷ          |

|   |                               |                         |                                       |                 |                   |                                           |                        |                                         |                       | Ŷ          |

|   | Nets                          | Δ                       |                                       |                 | Multi             | ole Pin                                   | On                     | a-Pin                                   | NC                    | Pin        |

|   | Nets                          |                         | All                                   |                 |                   | ole Pin<br>ets                            |                        | ∋-Pin<br>ets                            |                       |            |

|   | Nets                          |                         | ets                                   | cess.           |                   |                                           |                        |                                         |                       | Pin        |

|   |                               | Ne                      | ets<br>Acc                            | cess.           | N                 | lets                                      | N                      | ets                                     | N                     | Pin<br>ets |

| Т | ide                           | Ne<br>Total             | ets<br>Acc<br>1<br>16                 | 05              | N<br>Total        | ets<br>Access.<br>102                     | N<br>Total             | ets<br>Access.<br>3                     | N<br>Total            | Pin<br>ets |

| Т | ide<br>Top only               | No<br>Total<br>637      | ets<br>Acc<br>1<br>16                 | 05<br>0<br>0    | N<br>Total<br>102 | ets<br>Access.<br>102<br>100%<br>0<br>122 | N<br>Total<br>522      | ets<br>Access.<br>3<br>0.575%<br>0<br>9 | N<br>Total<br>13      | Pin<br>ets |

| Т | ide<br>Top only<br>ottom only | Ne<br>Total<br>637<br>0 | ets<br>Acc<br>1<br>16<br>1<br>96<br>2 | 05<br>6.5%<br>0 | Total<br>102<br>0 | ets<br>Access.<br>102<br>100%<br>0        | N<br>Total<br>522<br>0 | ets<br>Access.<br>3<br>0.575%<br>0      | N<br>Total<br>13<br>0 | Pin<br>ets |

Once the possible probe positions have been analyzed, the nail allocation algorithm selects the best of these opportunities for the nail positioning, according to the preferences set by the user.

This allows the estimated coverage to be calculated according to the real test access.

**TestWay Express** generates a complete set of documentation:

- Accessibility reports to provide a list of the nodes that do not have access, with reference to the rule placement violation that prevents access.

- Check plots and drill files.

- List of probes and nails in MS-EXCEL format.

- Nail retro-annotation back to the schematic. This is helpful for repair because it allows visualization of the nails on the layout, schematic and virtual schematic viewers with full cross-probing.

## SELECT MANUFACTURING STRATEGY

When deciding on the optimal test flow, it is important toconsider all available test and inspection machines, such as AOI, AXI, BST, ICT, FPT and Functional test.

The "test line" is defined using a simple drag and drop operation. The theoretical test models for coverage estimation and the actual test models for coverage measurement, can be combined to reflect your manufacturing strategy.

The gauges provide a quick view of the level of component modeling and board accessibility. To review the respective report, simply click-on the gauge!

| overage estima | tion for the credic | altester |        | 11.1 | Real coverage tr | om test program |                     |       | - in | Analyze     |

|----------------|---------------------|----------|--------|------|------------------|-----------------|---------------------|-------|------|-------------|

| diane          | 182                 | Palsa.   | 6      | ^    | THE OWNER        |                 | 1                   | -     | ^    | Mew apor    |

| 10 A           | and the second      | 200      | *      |      | 1                | 1 and           |                     |       |      | Close       |

| ACI            | APM                 | AXI      | BST    |      | e3Di             | acculogic       | asset               | bbc?  |      | Help        |

| 258            | 155                 | Call     | -03P   |      | 10000            | -               | Hall and the second |       |      | (TD)        |

| 20             | - AL                |          |        |      |                  | 5               |                     |       |      | 17          |

| hp_shocter     | fne_placer          | FPT      | KCT    |      | bsi              | cascon          | checksum            | cinis |      | Closefficat |

|                |                     | March 11 |        |      |                  | C 6500.000      |                     |       |      | A           |

| stine          |                     | d'attes  | 1157 2 | *    | - 13             |                 |                     | ASSO. | ~    | Probe       |

| ICT            |                     |          |        |      |                  |                 |                     |       |      |             |

| STOP B         | Se m                |          |        |      |                  |                 |                     |       |      |             |

|                |                     |          |        |      |                  |                 |                     |       |      |             |

| ICT            | gr228x              |          |        |      |                  |                 |                     |       |      |             |

## **COVERAGE ESTIMATION**

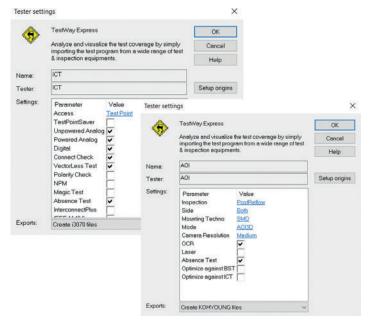

Each of the theoretical test strategies allows selection of tester settings, from a feature list for a particular test strategy.

In order to provide a more accurate estimation, any specific test features that are available on the target tester should also be included in the analysis. This aligns the estimated coverage to the real tester coverage.

**TestWay Express** handles cross optimization along the test line, such as Boundary-Scan or AOI, that can be used to minimize the cost of In-Circuit Test or Flying Probe Test.

## **DESIGN TO TEST**

The test strategy simulation results are used to automate the assembly, test & inspection program generation for assembly machine, in-circuit test (*ICT*), flying-probe, X-ray, Automated Optical Inspection (*AOI*) and Boundary-Scan test.

CAD2CAM converters are available for test & inspection machines from leading suppliers.

| CAD2CAM converter                                               |                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Assembly                                                        | Inspection: AOI<br>& AXI                                                                                           | Test: BST, ICT,<br>FPT, Wiring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| Assembléon<br>ASM (ASM<br>automation<br>Panasonic<br>europlocer | ALeacler CYBER OPTICS<br>Meret Annualse<br>Orbotech Saki<br>Vise Content<br>Ten Research Re<br>MarchNology VITrox* | ACCUGOSC<br>CHECUSSUM<br>CHECUSSUM<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>CORECLIS<br>C |  |  |  |  |  |  |

In addition to creating the test machine input files, **TestWay Express** also generates test models for analog multi-element components and digital models including disable configuration.

## **REAL COVERAGE**

The real test coverage is determined after the test has been developed and debugged, by analyzing the test program or coverage reports, from a wide range of test and inspection systems used within the industry.

Industry standard coverage metrics such as PPVS (*Presence, Polarity, Value, Solder*), or PCOLA/SOQ (*Placement, Correct, Orientation, Live, Alignment / Short, Open, Quality*) are used in calculating both the estimated and real coverage, so that the same analysis criteria is used in the overall analysis.

More than 60 coverage importers are available from the leading test and inspection suppliers within the industry.

| Coverage loaders                                                                                 |                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Assembly                                                                                         | Inspection: AOI<br>& AXI                                                                           | Test: BST, ICT,<br>FPT, Wiring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| Assembléon<br>ASM ()<br>MYDATA<br>automation<br>MICRONIC<br>Panasonic<br>Panasonic<br>europlocer | CYBEROPTICS<br>Mediatere<br>Corbotech OMRON<br>TRIBLER<br>SAKI VITrex*<br>Mitteret<br>SAKI VITrex* | ACCORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>CORCELS<br>C |  |  |  |  |  |  |

When combining theoretical tester models with the real test data. It allows direct comparison to verify that the completed test program is in alignment with the early expectations.

# **EXPLORE TEST COVERAGE**

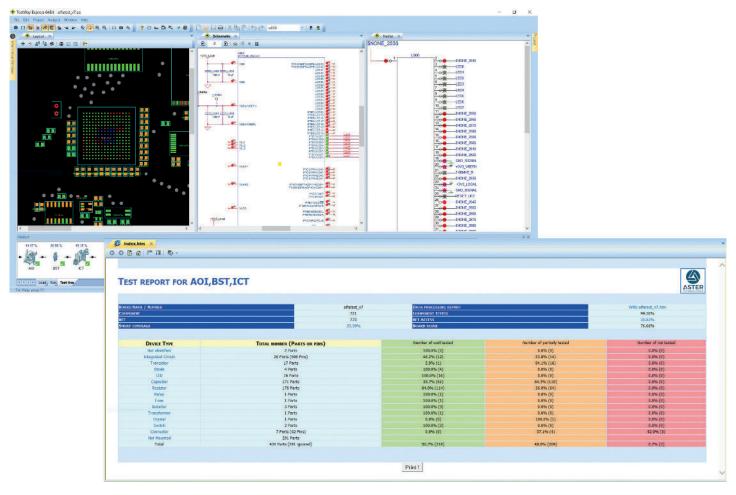

Once the test strategy is defined and the respective tester settings are selected, the "Analyze" button launches the analysis and displays the resultant coverage across all views and reports.

TestWay Express creates a variety of comprehensive HTML and MS-Excel reports.

- Board level overview of the combined coverage, or independent reports that define the coverage provided by each of the test and inspection machines in the test line.

- All components are categorized within the "Device Type" field. To access the pin level coverage, select the device category to drill down to the component list and select the respective device.

- The overall coverage is defined by the "board score" within the top level report. The individual coverage scores for the respective test strategies are highlighted in the test line.

- Individual test reports can be viewed by selecting the respective tester from the test line.

- Navigation is aided by full interactive cross-probing between all the HTML reports, the schematic, layout and virtual schematic views.

- Coverage visualizations are categorized using easy to interpret traffic light color coding.

# Visit www.aster-technologies.com for the latest product news.

Copyright © 2022 ASTER Technologies.

All other trademarks mentioned in this document are trademarks of their respective owners.

**Corporate Headquarters ASTER Technologies** 55 bis, rue de Rennes F35510 Cesson-Sevigne - France

Phone: +33 (0)2 99 83 01 01 Fax: +33 (0)2 99 83 01 00 sales@aster-technologies.com